第19回

次の開発テーマを模索中に今流行りのIOT関係に嵌りまして、早速アマゾンからESP32と言う小さなマイコンチップ内にWI-FIとBlurtoothの機能を持った小さな基板を購入して実験中ですが、驚く程簡単に使えるのと非常に安価なのでこれも時代の波かなと思いながら感慨に耽っている今日この頃です。

ESP32を使うためにはWindows 10に開発環境をインストールしてUSB接続で電源供給と共にプログラミング環境は高級言語のコンパイラーが付属しているので物凄く簡単に遊べます。作ったアプリもワンタッチでESP32に転送して動作します。周辺回路との接続はブレッドボートと言うジャンパー線を接続して使うため、ハンダごては必要ありません。学生の頃電子ブロックで遊んだ感覚で手軽に使えますが、弊社のアナライザーに組み込んでPCの代わりにスマホを端末に出来ないか模索中です。かなり前にESP32の存在は知っていたのですが少し馬鹿にしていました。ただESP32がWI-FIで接続出来ることは、これから先の計測器の端末として非常に有用なパーツとして浮かび上がる可能性が有ると思いますが、I/O処理がGPIO形式なので処理速度的に計測器のメイン処理には無理かなと思っています。ひと昔前ならばスマホ等に接続するには高度なソフトウェア処理が必要でしたので時代の波をひしひしと感じます。ただの通信用パーツとして捉えるならば非常に有用なキーデバイスです。これからの弊社の計測器の端末用として考えて実験中です。ただ大事な事は、WI-FI通信用デバイスと制御装置とは完全に切り離す必要が有ります。インターネットは便利ですが昨今の事情を考えると他からの介入によってシステムダウン、データの消失等を考慮する必要が有りますのでここが怖い所です。

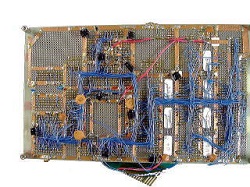

ブレッドボードを利用したテバッグの様子です。構成は、ESP32とMCP23S17と言うSPI通信でシリアルパラレル変換デバイス、そして以前購入した雑誌に付録でついていたFPGA開発キットでMAX10が搭載されているデバイスです。なぜSPI通信かと言うとESP32は、GPIOで周辺デバイスと接続するのに作るものによってはI/Oの本数が少ないためI/O拡張のため使用しています。これをどう使うかはこれから考えます。参考までに写真を添付します。

次から次に新しいキーデバイスが誕生しますが、ひと昔前に比べて安価なのと入手し易いのが良いですね。製品開発するには時間とお金が掛かりますが、時間は寝る間を惜しめば何とかなりますが、開発費は逆立ちしても捻出出来ません。開発環境を含めてキーデバイスが安いのは大いに助かります。

第18回

前回のお話で、これからの電子回路設計は、たたき上げの技術では無く正統派で学んだ数学が必要です。

ハードウェアもソフトウェアも数学の素養無くしては、設計出来ない時代が来るとお話しましたが、ただいま遅まきながらこれらの技術に必要不可欠な虚数と複素数について勉強しています。学生時代は虚数なんて何の役に立つのか考えもしませんでしたが、今は必要性が分かります。専門的になりますが、デジタルを用いた無線通信の世界では無線部は、微細化した半導体で非常に高い周波数に対して格段に性能が向上しており、その他の部品の微細化により、フロントエンド部は、周波数が高いだけで原理等はアナログで動作しています。そこから平衡変調された信号を取り出して大規模集積回路のI・Q信号としてデジタル部に渡されて大規模集積回路でCPU、多数の乗算器と特殊な演算回路等が組み込まれて、ここでハードウェアによる演算が行われて実際の映像信号、音声信号、データ信号として人間の目、耳にに触れる信号となります。虚数と複素数は、この復調に於いて重要な数学的要素となります。数直線で表現できない数値を表現するために虚数を用います。これを用いると何が便利か。簡単に説明すると虚数を用いると三角関数を用いるより、もっとも簡単に第一象限から第四象限までのx,yの座標を求める事が出来るのです。この性質を利用することによって高速に演算が可能になり、リアルタイムスペクトルアナライザーが小さく高精度で設計できるのです。昔は、大型のゴミ箱位の大きさがありましたが、今はUSBドングルに収まる大きさで実現されています。ただただ驚くばかりです。私が今回驚いたのは、虚数の説明で数直線上に表せない数値を以下にして表すかを何百年前の数学者が既に駆使していたことです。私の数学の探求はこれからも続きます。

第17回

私は、この歳になって数学の素養が無いことが悔やまれてなりません。現在開発しようとしているアナライザーの機能にどうしても装備したい機能がありますが、実現させるのに大きな壁になって、立ちはだかっているのです。

私の泣き言を聞いてください。頭で原理は、理解しているのですがアナログ回路での理解ですので、FPGA内に組み込む事ができない、このもどかしさです。私は、小さい頃からラジオ少年でした。アマチュア無線もやりました。ラジオ少年は、その後インテル社が世界初の4ビットマイコンを販売して、私はそれを組み立てて喜んで遊んでいましたが、その後すごい勢いでデジタル全盛期になり、現在デジタルおじさんになりました。論理回路では、仕事としてかなりのシステムを構築してきましたが、今回の開発案件だけは、難しすぎて二年間思考錯誤して研究課題となっています。たくさんの文献を読み、ネットで調べても未だに明確な道筋が見えないのです。この事で私が理解している技術は、広帯域のスーパーヘテロダイン受信機の回路で、局発と言われる回路を掃引して色々な周波数を受信できるラジオなのです。

この方式は、特殊な超高級と言われる計測器では健在なのですが、普段では今は使われていない技術で、その代わりに数学的手法でFPGAで実現しているそうです。もちろん、フロントエンド部には高周波アナログ技術が必要ですが、あのチップ内にアナログ回路では、考えられないほどの小ささで収まって調整がし易く高性能を実現していることに驚きを禁じえません。この技術は、全盛のスマホ、デジタルテレビ等の基本となっていますが、その回路技術が理解できない私は、過去の遺物となりつつある事に悲しみさえ感じます。何とかして理解しなければ・・・焦ります。

この技術は現在ソフトウェア無線と呼ばれています。物の本によれば米国が握っている技術だそうです。

私が弊社の計測器に装備したい機能は、信号とノイズを分離して伝送系のノイズ成分を分析して通信エラーの原因ノイズを特定したいと思っています。なぜならば、最近弊社の試験環境で実施している製品評価試験、製品出荷試験等で空間ノイズの増大で エラーが頻発しているからです。お客様も機器の不具合なのかノイズなのか判断に迷うと思います。

この機能を備えれば、ノイズ源を特定して対策が講じ易いからです。開発に取り掛かるのはいつになるか皆目検討がつきませんが、目下研究課題です。頭が痛いです。久々に弱音がでました。

世間一般では、この機能をスペクトラム解析といいますが、私の頭の中では未だにスーパーヘテロダイン受信機の局発掃引のままです。この技術開発には、高度な数学の素養が必要で、FFT または、フーリェ変換とも呼ばれています。

論理回路の設計技術と数学的手法で設計する技術は、別物ということを悟った今日この頃です。

これからの電子回路設計は、たたき上げの技術では無く正統派で学んだ数学が必要です。

ハードウェアもソフトウェアも数学の素養無くしては、設計出来ない時代が来ると思われます。

第16回

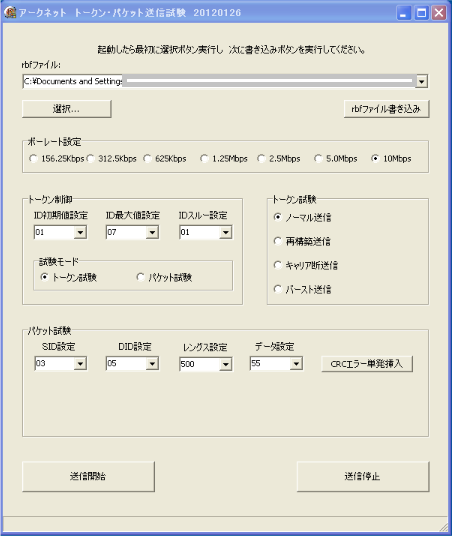

今回は、弊社がARCNETプロトコルアナライザーの設計・開発を行う際の開発環境をどのように構築したかについてです。

計測器等は、お金を払えば揃えられますがお金を払っても調達できないもの、それはARCNETの試験用信号源です。簡単には、ARCNET LSIを使ってシュミレーターを作ればそれなりの試験は可能です。それは最初に作ってみました。簡単な試験でただの送受信のデータを解析するのはこれで充分です。

しかし、アナライザーとしての受信性能試験、つまり、どの位の間隔でパケットデータを送っても取りこぼすこと無く受信可能か? CRCエラー試験は、パケットデータの最後に付くCRCコードを操作する必要がありますが? パケットデータ送受信試験で、パケットデータの内容とレングス長を簡単に任意に設定できる必要がありますが? 再構築の試験は、再構築を発生させるためトークン信号の操作の必要性がありますが? バースト検出回路の試験は、バースト信号の発生が必要ですが? ノードマップ試験等で必要な最大ノード数255台の確保は不可能ですが? 全ノードに対するパケット受信性能試験を行うことも必要ですが? 全ボーレートでの受信試験の必要ですが? これらの試験は、実ノードを使用しての試験は物理的に不可能なので・・・

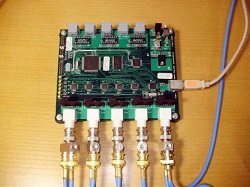

作ってみました。上記の試験をすべて適える試験装置。弊社旧製品のハードウェアを使ってハードウェアシュミレーターを作ってみました。ARCNET LSIが出力するプロトコルの送信フレームをFPGA LSIで、忠実に再現して上記の試験信号をハードウェアで実現しています。ここからソフトウェアシュミレーターでは作れない特殊な信号パターン、エラー信号等を送出してアナライザーの挙動を試験します。

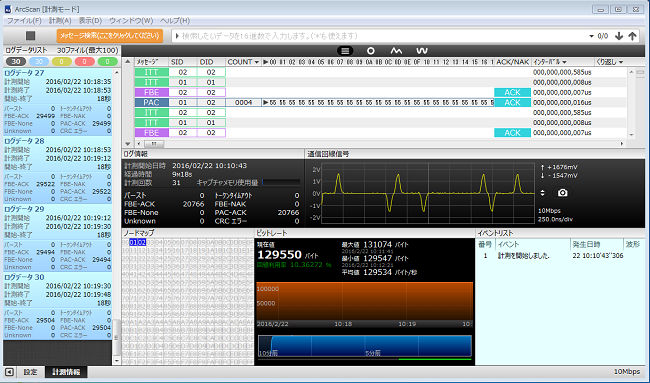

下記の図は、ハードウェアシミュレーターからノード数を255台接続して受信するノードマップ試験です。弊社アナライザーのトークン受信性能試験の検証結果です。これもあり得ない接続ノード数ですが・・・

下記の図は、弊社製[ArcScan]アナライザーを使用して受信しているARCNETプロトコルは、弊社製ハードウエアシュミレーターを使用して秒間129,550バイトでパケットデータを受信しています。実際のネットワークではあり得ない速度で受信しています。通常ARCNET回線利用率は2%位ですが弊社製品は回線利用率は、10%を超えていても受信可能です。送受信ともハードウェアで実現しているからできることです。弊社の取りこぼし無しに対する設計思想の結果です。参考までにノードが175台存在するような重い負荷の場合であってもトラフィックがトークンパスに要する時間の2%以上に達することはほとんどないそうです。

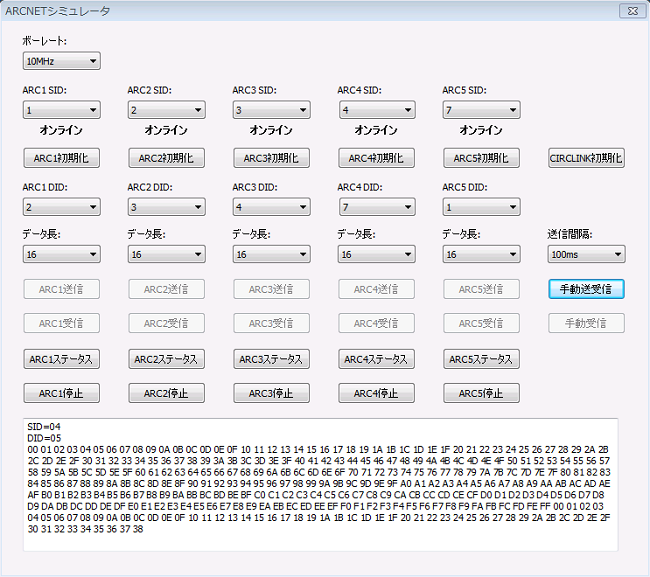

また、簡易試験装置としてARCNET LSIを5個使用したソフトウェアシュミレーター本体装置とソフトウェアシュミレーター試験システムをご覧ください。下記に示すソフトウェアシュミレーターシステムコンソールによってARCNET信号を制御・出力しています。<ArcScan>の取扱説明書の表示画面例とホームページの表示画面例は、ソフトウェアシュミレーター信号によって製作されています。パケットレベルの試験と製品出荷ヒートラン試験には重宝しています。

本体装置

試験システム

第15回

前回の続きで恒温槽の写真をご覧ください。このオーブンの本体は、安いだけあって筐体はペラペラの鉄板で出来ているため制御回路を組み込むスペースも熱遮断できるスペースも有りませんので木の板に制御回路を組み込みました。この木の板に温度コントローラー、トライアック制御回路、ACアダプターを接続しています。このオーブンは、消費電力800Wのヒーターが内蔵されていてスイッチによって800W,400W,200Wと切り替えられるようになっていますが、今回の仕様では、この切り替え回路の配線等をすべて外して使用しています。ヒーターは、200Wでも熱容量が大きいのでトライアックを用いて70W位に制御して使用しています。左の写真の左側にあるアルミ製の筐体に入っていてボリュームが付いています。ファンは見えませんが、オーブン内の後方にねじ止めされております。また、内部にサーミスターの温度センサーを固定して配置されています。このセンサー信号は、写真右側の温度制御ユニットに入力されていてヒーターをON/OFF制御しています。このような簡単な制御でも40℃から80℃までは±1℃の精度で温度設定が可能です。オーブンの容積とヒーターの熱量、そしてファンの風量のバランスしたところが高精度に設定できるポイントです。今回は、取り敢えず急いで製作する必要が有りましたので雑な作りになっています。本来ならば二重構造のケースに組み込んで作れば立派に見えるのですが妥協して作りました。また、すぐに取り出して使えるようにオープン内には、同軸コネクター、USBケーブル、5V電源の配線を予め配線しています。初めて製作した恒温槽に性能は満足していますが、温度が一定に達するまでの時間の短縮(風量の可変、ヒーター熱量の可変、比例制御等の技術が有ればもっと高精度制御も可能と思いました、本機には、無人でも安全に運用するため低温の温度ヒューズが必要ですが、まだ実装していません。近々実装する予定です。また、右下の写真は、後面で電源の他 信号ケーブル等の引き出しが見えています。この位の環境試験用恒温槽は,有ると電子機器の温度試験には重宝します。しかしこのオーブンは、¥980円で本当に安いですね。ただ作りはすごく雑です。一回ばらしてしまうとタッピングビスは、鉄板の厚さが薄いためタッピングビスがスカスカになります。温度コントローラーは、英国製で高性能です。温度センサーさえ選択ミスしなければ中々の性能を発揮します。細かい設定も可能です。

第14回

今回のテーマは、恒温槽の製作について書いてみます。去年の秋ごろに温度試験を行うのに急に恒温槽が必要になりました。それまでは、ドライヤーで温度を測りながら電源ON/OFFで約60℃をキープして実験していましたが、長時間の試験が必要になり、商社に問い合わせても納期・価格等が合いません。稼働率の悪い装置は、なかなか購入できません。装置サイズも大きいし、仕方なく自作する事にしました。ケースは、通販で購入した輸入品の家庭用電気オーブンで新品で¥980円、そして肝心の温度制御装置、通販でイギリスからの輸入品で¥6,000円位で一番高い部品、あと小物パーツで¥3,000円位でした。たかが温度制御侮れません。一番肝心なことは、ヒーターの熱量と風量であることが実験的に分かりました。ヒーターは、オーブンに付属している物を改造して使いましたが試行錯誤しました。そして風量 これは、通販で購入した普通のパソコン等に使用されている物と同じですが24V仕様です。恒温槽の容量に関係してヒーターの熱量とファンの風量は、深い関係が有り、勉強になりました。結果的には40℃から80℃までは±1℃の精度で温度設定が可能です。この装置のお陰で温度試験が楽になりました。恒温槽の製作についての技術的なお話は、次回の技術余話に写真等を掲載して説明します。

第13回

新年明けましておめでとうございます。本年も宜しくお願い申し上げます。

去年 この技術余話を書く時に思ったことは、この先の日本の電気業界の衰退の様子を見て鼓舞して終わりましたが、ようやく暗闇を抜け出してグローバルリセットの負の長いリセット期間が終わりプラスに転じる可能性が出てきました。異常に長いリセットパルスは、色々な悲しみや苦しみを生みましたが、新たな再生を願って古いものや、過去の遺物と化した組織、習慣を打ち壊し日本の電気業界に渇を入れて成長路線に乗って大躍進する希望が出てきました。電機業界では、付加価値の高い製品で世界を席巻する日が再び訪れる予感がします。日本人は、昔から勤勉で向上心に富み創意工夫でよい製品を開発する能力があります。資源の無い国でこのような発展を遂げた国は、日本以外ではありません。まさに知恵だけで生き抜いてきた日本の科学技術です。途中 電機業界も極端なコストダウン化を追及してアジアの新興国に敗退して現在に至っています。他と同じものを作っていては またコスト競争に敗れるのは明白です。このような単純な図式は誰でも分かりますがそれを実践できない大企業の基本技術の低下と知恵を結集出来ない組織の陳腐化 そして目先の利益だけに固執する経営者と中間管理職 誰も傷を負わない戦争は無い! これは経済戦争で死人こそ出ませんが立派な大戦です。弱肉強食の淘汰は、現在進行形で進んでいますが、これももう少しで終焉を迎え本当の春 つまり春に草花が一斉に芽吹く百花繚乱が再び訪れる気がしてなりません。新年にあたり希望を書いて見ました。今年もがんばろう!!!!!!それでも例外企業としてトヨタ自動車は立派ですね。日本の誇りですね。ちなみに車は、カローラに乗っています。壊れない 安い かっこいい(?)・・・・

第12回

新年明けましておめでとうございます。本年も宜しくお願い申し上げます。

二年がかりで製品開発をやって やっと終わりに近づいていざ販売の段になると電機業界のすさまじい不況といいますか だましだましきたこの業界の歪が一気に噴き出して企業の赤字決算のオンパレードで販売がぱったり止まりました。こりぁ開発ばかりしている場合じゃないと慌てている私がいます。しかし政権交代した政党の掛け声一つで円高誘導、株価上昇で年末から業界の勢いだけは盛り返してきましたが これが本物でもこの先も安定して電機業界に活気が戻るかと言うとそれも難しいと思う。大量リストラした事によって会社の技術力が分断されて取り戻すのに時間が掛ると思うのです。大企業の下には関連した仕事を行う中小企業がたくさんぶら下がっていますが、その中小企業も泣く泣く人員整理した会社がたくさんあります。中小企業ほど人によって支えられていますから技術力を回復するのに時間がもっとかかります。そして部品関係は、もっと淘汰され始めていて小さい商社は、倒産、事業所閉鎖等で部品購入も思い通りにならなくなっています。これからの日本の電機業界はいばらの道を暫く歩かなければなりません。しかし考え方をかえると これはチャンスかもしれません。なぜかと言いますとこれはハードウェアで言うリセットなのです。人間の活動は、ある程度まで進むと効率が悪くなり仕事をまじめにしなくなるというよりも仕事をし難くなります。硬直化です。なぜし難くなるか? 企業でも人でもしがらみが増えるからだと思います。このしがらみを解きほぐすのは容易ではありません。グローバルなリセットが必要なのではないでしょうか? 今回グローバルリセットが入りました。そう思う今日この頃です。今年も頑張るぞ 一人気合いを入れてる私です。貴方も頑張ってください。みんなでがんばりましょう・・・・・

第11回

新製品開発と雑用に追われて一年間更新しなかった事をお詫び申し上げます。振り返ればこの一年 不景気と震災で日本経済は、ガタガタになり弊社も潜望鏡深度でじっと耐えていました。しかし売れないおかげで新製品開発と実験には全力を注げました。私はハードウェア開発技術者ですから特に通信アナライザーの物理層の検証とか観察を重視します。その第一歩が波形観測です。オシロスコープ機能です。ようやく技術的にも解決して本格的に量産試作の段階に来ました。汎用のFPGAによってデジタル技術は飛躍的に楽になりましたが、アナログ技術はそれほど楽にはなっていません。A/D変換チップは、高速のチップで少しは楽になりましたが電源の問題、パスコンの問題、デジタルノイズの混入とプリント基板のパターンの引き回しの問題と枚挙に暇がありません。それらを一つ一つクリアしてほっとしている今日この頃です。

それと もうひとつの悩みの種が試験装置の開発です。弊社で開発している通信アナライザーは汎用的では無いため専用の試験環境は存在しません。通信環境を普通に構築するとノードの数から大変大袈裟な物になってどちらが開発品なのか本末転倒になってしまいます。そのため製品ボードのFPGAを利用して論理的にノード数を増やして試験環境としています。自在にエラー信号等を作り出せるので大変重宝しますが、製品開発並の時間が掛かります。通信アナライザーの開発は、思ったほど利益にはなりません。とほほ・・・・それでもやるのは面白いからです。ただ それだけです。購入して頂いたお客様の声です。その声とは ほんとだ・・・教科書通りのプロトコルで流れてる・・・あたりまえですが・・・励みになります。もっともっと勉強しなくては。

つい 先頃のお話ですが、某社様に製品のデモの要望があり訪問しました。技術の方々は通信アナライザーの存在を知らなかったようですが、やはりプロトコルがリアルに見えると大変喜ばれます。こちらもうれしくなって知りえる限りの技術的なお話をさせて頂いてお互いに満足のいく訪問デモになりました。これこそが大事な事だと思いました。お客様の知りたい事、開発メーカーの知りたい事がその一時間弱の間に情報が満載されているのです。開発の時間を割いてこれからは、もっと訪問してみようと思いました。とりとめのない話をしてしまいましたが次回は、技術的な話をしたいと思います。

最後に技術余話(10)で紹介した基板をケースに合わせて再設計した最終基板と簡易版試験装置の写真をアップします。

第10回

今回は、前回に引き続きアートワーク失敗例を解説致します。左の写真 上の赤枠は、見事!? 大失敗のQFNタイプのUSB 2.0 LSIの部分でその右側にクローズアップがあります。前回 説明しましたが、このLSIは、底面に放熱を兼ねたGND電位サーマルパッドが有りそこを避けてスルホール・ランド・パターン等を配置しなければなりません。しかしLSIのピンの内側にたくさんのスルホールが有って実装不可能でした。・・・・・・ううっ 悲しかったです。

もうひとつの赤枠は、電源系の失敗です。+2.5Vを取り出すのに+3.3V電源から降圧したため 多少不安定だったので+5V系に変更しました。LDOタイプに変更すればジャンパーは不要ですが、+3.3V系の負担にならないようにしました。そして 試行錯誤の末 下の写真の様になりました。今回の写真には掲載していませんが、これの改修と一緒にARCNETシュミレータを増設したため地獄の様なデバッグなりました。CPUクロックが40MHzで動作している回路は安易にバスを外に引きだしては回路の不安定さが増すと同時に高速アナログ回路も配線で引き延ばす事になり最悪の結果になりました。配線に長さに注意しながらUSB 2.0の改修は写真の配線で動作しており単体では、ほぼ問題無く動作しています。それ以上の増設は、バスバッファの挿入で対処してARCNETシミュレータ共々現在は、完璧に動作しております。これが私の初めての高速回路のアートワークでの失敗談です。この編は今回で終了します。

失敗基板

第9回

アートワークが完了して基板製作に入った事を前回お知らせしましたが、今回は、基板が完成して部品実装とその後のハードウェアデバッグ等を通じて失敗した例をお知らせします。参考までに部品実装した写真を示します。大きな失敗は、今回 USB 2.0 480Mbpsホストインターフェース用として56ピンのQFNタイプのLSIを搭載しましたが、このLSIは、底面に放熱用の金属が露出していてGNDに接続するような仕様になっていたため 目も当てられない結果となりました。実はこのLSI直下にスルホールが何本もあってショートするので基板に実装できないのです。この対策に一カ月間掛かりようやく結論を得ました。バスラインを配線で延長してこのLSIを搭載するサブ基板を製作してデバッグしましたが、動作の不安定さで断念。もう一回GND周りを強化して再度挑戦しましたが、所定のCPUの速度で動作しない結果となりあきらめました。このLSI以外の回路は、問題無く動いています。反省点として実装部品の仕様を良く確かめてアートワークしないと泣きを見ます。因みに この回路は、USB 2.0 480Mbpsの回路ですのでかなり高速の範疇に入ります。弊社 USB アナライザーは、メーカーですので売るほどありますから測定し放題でしたが、USB回路は、やはり測定器が無いと何がどうなっているのか雲を掴むようなデバッグになります。たくさんの面白い現象に出くわして四苦八苦しました。USB 2.0 は、認識したらデバッグ完了ではありません。大量のデータを流したら ホストがハングアップしたり、PING->NAKしかない転送をしていてあたかも転送しているように見えます。これが大きな間違いの元です。とにかく状態が千変化して楽しませてくれます。とてもじゃないがアナライザーが無ければデバッグは無理です。・・・・弊社 アナライザーメーカーですので少し宣伝しました。あと デバッグ中に感じた事は、試作レベルでは強力なGNDのランドを用意しておくとデバッグがやり易いと思いました。またQFPのランドは、自分で実装する場合、少し長めがハンダ付けし易いです。QFNも自分で実装する場合 長めにしましょう。また 部品の取り外しの事を考えたら、サーマルレリーフは必要ですね。高周波的には反する事ですが実感しました。シルク印刷は、スルホールを避けないと文字がかすれます。実感しました。また CADの自動配線は、非常に便利ですが、かなり修整したほうが後で泣きが少なくなります・・・・・泣きました。・・・・ただし 非常に有能です。・・・・修正に少しセンスを要します。次回は、もう少し詳しくレポートしたいと思います。今回は、めげています。 まあ 一回目のアートワークを点数にすると75点です。もちろん100点満点中です。すごく勉強になった事とこれから自由自在に安く基板が作れる自信が付きました。回路を思いついたら即基板化してデバッグが可能になります。次回は、搭載出来ないLSIを無理やり搭載してデバッグの結果をお知らせしたいと思います。

第8回

第8回 今回は、自分の回路を自分でアートワーク化して基板入荷待ちまでを書いて見ようと思います。今回 自分でアートワークをして見ようと思ったきっかけは、アートワーク代が高いと思うのと、設計者がアートワークする事によって理想的な基板を作る事が可能だと思った事。そして不況の影響で暇な事です。・・・これが最大の理由ではありませんが(笑)。満足のいくアートワークまで練習を含めて約半年掛かりました。でも一度やると次からは簡単です。アートワークの内容は、SH2のCPU、512KByteのSRAM、ARCNET,CircLink,128MByteのSDRAM,USB 2.0 Hispeed回路、アルテラ サイクロンⅢ、160Mbpsの高速A/D変換回路と素人にとってはかなり高密度な回路のてんこ盛りを載せてしまいました。因みに アートワーク代の見積を取ると60万円位取られますょ。そして半導体関係の調達は、インターネットで海外二社からと国内二社から調達。なぜか 国内より少量でも安いです。便利な世の中になりました。そして早いです。米国へ注文して四日間位で入荷します。基板は、四層板で寸法は、182mm×157mmです。試作基板の費用は、四枚作って約¥45,000位です。これもインターネットで注文して海外で作ってもらうので非常に安いです。

この記事を書いているのは、基板入荷四日前ですのでまだ動いていません。失敗したら次回 急にテーマが変更になりますので分かります。参考までにアートワーク図を掲載しておきます。次回 部品実装して写真を掲載する予定です。

ただし 私の経験上 一回目の基板化は、時間がかかります事を申し上げておきます。十回位アートワークし直しました。そのかわり段々上手になります。何事も訓練です。心配で心配で中々基板作成に踏み切れませんでした。納得が行くまで試行錯誤の連続です。

第7回

今回は、ARCNET,CircLinkプロトコルのスーパアナライザーのベース基板作りに励んでいます。何がスーパーアナライザー何だろうか?それは物理層の異常検出を重視した設計となっています。普通 通信ネットワークは、物理層と論理層で構成されていますが、明確な定義があるネットワークと明確に定義されていないネットワークがありますが、大まかに分けるとコネクター、ケーブル、メディア・トランシーバ、通信制御の最下層プロトコル等です。ここで不具合が発生すると従来の測定方法ではデータストリームを高速にメモリに保存して計測停止後に先ほど保存したメモリ内容をソフトウェア的に絞り込んで原因を見つけますがソフトウェアの方式では間接的に不具合をトレースする事になり原因を探りにくく時間が掛かる事が多くデバッグするのが非常に困難でした。

物理層のデバッグ手法として信号波形の確認、レベルの確認、ノイズの有無、タイミング等を観測するのが不可欠です。これを観測するのにオシロスコープを必要とします。今回は、大胆な設計・開発を目指してアナライザーに160MHzサンプリング・デジタルオシロスコープを装備していつでも波形観測が可能なりました。(非常に高価格のアナライザーにしか装備されていません)ソフトウェアデバッグ時に同時に物理層の確認が容易になりました。また物理層の異常検出をリアルタイムで行うため、FPGA内部に必要な物理層異常検出回路を組み込み異常信号を的確に捉えられる様に研究・開発しています。

要するに今までリアルタイムで検出出来なかった、リコンフィグレーション検出、バースト検出、ノードID不一致検出、CRCエラー検出,メッセージ1バイト目のコードに違反した信号をリアルタイムで検出します。

また物理層の巡回信号は、間断なく流れていて従来は、取りこむ事ができませんでしたが、大幅な仕様変更と大胆な回路構成で全通信信号をハードディスクに保存する事が可能になりました。

また データストリームのトレンドを正確に記録するため ハードウェア・タイマーとカウンター回路を駆使した極めてハードウェア志向の強いロジック回路を組み込み、オペレーターに、よりリアルに正確な情報を通知する事が可能な精細なグラフを表示します。これらの構想は、約10年前から有りましたが、今回不景気のおかげで着手できました。人間暇な時も必要です。つい忙しいと目の前の現実に追われて取り合えず売れる物を作ってしまうという商業主義に走りますが、今回は、不景気のおかげでじっくり開発できました。もうひとつ おまけにアートワークまで手を広げて高速A/D変換回路、高速SDRAM回路を含む試作基板を製作中です。

このアートワーク設計の話は、次の技術余話に掲載予定です。高速ロジック回路と高速アナログ回路は、ハードウェア設計者がアートワーク化したほうがコストが安くて性能が良いと思います。ただし お断りしておきますがパターンは汚いです。念のため申し添えておきます。スピードの遅い回路は自動配線を行うため芸術的ではありません。実用的です。

手配線で組んだ試作回路の写真を示します。この試作回路を自社でアートワークして基板化します。

この次からの試作は手配線ではなくすべてアートワークして基板化する予定です。

回試作中のスーパーアナライザーボードでCPUボードと雑誌付録のFPGAボード、USB 2.0 480Mbpsインターフェース回路、160MHzサンプリングA/Dコンバーター、6chアークネットシミュレータ回路、1ch CircLinkシミュレータ回路と弊社製品ポードを裏面で手配線で試作しました。ほぼ動いていますが、高速A/Dコンバーター回路は、少しノイズっぽい波形です。

高性能アナライザー試作基板の様子

第6回

今回のテーマは、ネットワークシステムの物理層と不具合についてお話します。最近 納入後のシステムでネットワーク不具合が発生して、その対応に迫られ四苦八苦されている技術者が増えています。それも物理層の潜在的不具合が絡んでいるのでバグなのか、ただ単なるハードウェアの不具合なのか簡単に切り分けが出来ないところに難しさがあります。お客様にご迷惑を掛けるのは勿論、社会インフラシステムならば多くの人々に迷惑をかける結果となります。多くの場合、その背景には、システム納入時の試験・評価の甘さがあるような気がします。納入前に充分な試験・評価を実施できない要因は、多々ありますが組み込み系のネットワークシステムの場合、システムのおまけとしか思っていないふしがあります。主機能のデバッグに気を取られて納入日間際になって慌ててネットワーク試験をしたら多少不安定だけれども納期との関係で出荷したらあとからクレームの嵐となるケースを多く見受けられます。ネットワークシステムの物理層は、設置環境によって特性が大きく変化します。ネットワークケーブルだけを取っても装置間距離、終端の位置、他のケーブルとの併設、その空間の電気的ノイズ環境、工事業者による敷設ケーブル特性違い、考えたらきりがありません。お客様からのご相談を受けて感じることは、どんな小さなネットワークシステムでも必ず仕様に沿った動き、信頼性、品質があるかどうか動作試験だけで終わらせないで測定器による評価試験をして出荷すべきだとつくづく思います。ネットワークシステムは、無線、有線に関係なく物理的にノイズには弱いものです。それをリカバリーする機能を多少は持っていますので余程設計が酷くない限り安心なのですが、そのリカバリー機能はもしもの備えとして考えて頼らない設計をすればよりネットワークシステムは強固なシステムとなり、安心して出荷することができます。もうひとつは、設計者がそのネットワークシステムの物理層を理解せずにネットワークシステムを構築した場合、必然的にトラブルは発生しますが解決するまでに時間がかかり過ぎます。理屈がよくわからないので完全な改修したかどうかの判断さえつかず、ずるずるとした改修作業になり技術的な信頼を低下してしまいます。弊社 アナライザーメーカーとして申し上げる事は、不具合が発生したらアナライザーを購入するのではなく、仕様作成段階から準備しましょう。そうすればデバッグ中にアナライザー等の測定器を使いこなしているので万が一不具合発生しても迅速な対応ができます。

また 普段からアナライザーの画面に慣れていればアナライザーを接続して事象が発見されれば即解決することも可能です。近年の不景気の影響で技術者が退職されたりしてそのネットワークシステムに詳しい人がいないのでアナライザーメーカーに助けを求める例も近年増えています。

我々も何とかして上げたいと思いますが、自分の設計した製品でさえ数年でうろ覚えになるのに別の方の設計されたシステムを短期間に理解することは極めて難しい事です。助言はできますが、それ以上の事は、現実的には不可能です。そのシステムを担当された方がしっかり現状を把握して そして助言を求めるのが最短の道と思います。次回のテーマーは、またまた 手配線の基板で次期新製品のモデルとなります。

第5回

今回のテーマは、試験環境についてお話します。弊社は、通信アナライザーのメーカーですが開発中に一番悩む事があります。それは,如何にして実ネットワークシステムに近いネットワーク環境を構築出来るかです。特にノードが多いネットワークシステムでは物理的に不可能なケースがあるため、ここで一番悩みます。今回は、ARCNETアナライザー オートログでの弊社の試験方法について解説したいと思います。オートログ機能とは、計測開始したら、ひたすら実時間情報と共にパケットデータを取り込んで制御用PCに保存する機能ですが、アナライザー側は取り込んだデータを解析してそれに実時間情報を付加する訳ですから時間が掛かります。その結果オーバーフローする可能性は高い事になります。しかし これを試験するのに大量のノードを用意するのは現実的ではありません。そこで弊社は、ARCNETプロトコルを高速に送出する事が出来る高速シュミレータを開発して取り込み限界性能試験、CRCエラー、FBE->無応答、PAC->無応答と言う実システムでは、なかなか再現できない異常状態を任意に作りだすハードウェア・ノードシュミレータをFPGAとDRAMを組み合わせて試験に利用しています。もっともアナライザーのハードウェアを利用してそれにトランシーバーを取り付けただけですが・・・・・・

ノード数は、255ノード、パケット送出の出来るノード数は 255ノード、もちろんトークンも廻ります。ソフトウェアで設定したシーケンスで送信しますので送信タイミングもある程度自由です。それをARCNET アナライザー オートログの詳細な試験に利用しています。シュミレータというとそれぞれのネットワーク用のLSIチップで実現する場合が多いのですが、測定器の評価には、使い難い部分もありますので、このような方法も少し開発に時間は掛かりますが、柔軟な試験環境として重宝します。また物理層の異常を再現する手段としても利用価値がありますので、興味のある方は、作ってみては如何でしょうか。何 そんな時間は無い! ごもっとも。しかしネットワークシステムは、納入前の試験は、徹底的に行ったほうが、後々楽です。トラブルで現地に赴いて現象再現まで待って、再現すれば良い方で、再現しなければ後ろ髪を引かれる思いでそこを立ち去る不安感、そしてお客様の不審感。見てきたような描写ですが、私もかつてはそうでした。再現しないと後味の悪い出張になります。それを一掃するのが試験であり試験環境です。

第4回

今回は、アプリケーション開発とこれからの技術者のあり方のお話です。弊社製品のアプリケーションソフトは、Delphiで記述されています。私は独立するまでは、アナログを含むハードウェア設計を担当しており、趣味の範囲でソフト開発をしておりました。しかし 以前いた職場で、自らがアナライザーのアプリケーション開発の必要性に迫られ、そのため以前から関心のあったDelphiで開発しました。この言語は、少しマイナーな印象ですが、アプリケーションソフトの開発にはピッタリです。意外と細かい記述が出来る割りに制約が少ない言語で、動作速度は驚く程高速です。言い換えればハードウェア設計者が自分のハードウエァ試験ツールを作るのに適していると思います。それで試験ツールでは勿体無いので製品版のアプリケーションソフトまで作ってしまいました。計測器は、ハードウェァの基本性能をギリギリまで引き出す必要があり、ソフトウェァアによって細かいハードウェア制御を必要とします。それとこの言語で開発すると見た目も非常に美しく表現できるので(作る人の感性にもよりますが)ハードウェア技術者の試験環境構築ツールには必須だと思います。世の中のほとんどのハードウェア技術者は、ほんのちょっとした試験ツールもソフトウェア担当に任せてあそこが使い難いの、ここのイメージが違うのとか言っている人に限って自分の作っているハードウェアの基本的な試験はほったらかしにしてやれソフトウェアの出来が悪いとか、仕様どおりに作ってないとか文句を付ける人の多いこと。自分の作ったハードウェアは、自分の技量で試験をすると自分の技量が良く分かります。そして何よりも重要なのはハードウェアとソフトウェアのトレードオンの極意が分かります。弊社のお題目のトレードオンの設計は、ここからきています。これからの開発は、すべてではありませんが、ハードウェア技術者がこの先シームレスな開発環境を手に入れて両方やる時代がきます。そのためにも今から訓練しておきましょう。リストラされないために。デメリットもお伝えします。仕事量は確実に増えます。プロジェクトが増えれば増えるほど自分の首を絞めます。しかし仕事の好きな方?は、良い部下を育てることです。そのためには部下に手本を見せることです。そういう先輩が減りました。なぜならば先輩諸兄も仕事に追われて余裕が無いからです。会社の体質にも原因があります。そのような場合は、転職をお勧めします。体を壊しては、元も子もありません。自分の身は自分で守らないと、現在の会社組織は、疲弊して誰も貴方を守ってくれません。昔は良かったと思います。すべてに余裕がありました。この十年で会社組織は悪い方向に向かい、不景気で会社の軌道修正もままならない状態です。せめて自分だけは犠牲にならないようにスキルと精神性を高めて乗り切りましょう。

第3回

今回は、測定器のお話です。御社のハードウェア開発環境の設備は充分でしょうか? 私は、このハードウェアの初期開発段階では、100MHz帯域のオシロスコープだけでした。ところが今回使用しているSDRAMは、クロック125MHzで動作しているので100MHz帯域のオシロスコープでは、繰り返し波形は良いのですが、ストローブ等の細い波形はよく見えません!!まともな波形として表示しません。困った挙句 中古でも良いから広帯域オシロスコープを入手しようと3週間ぐらいYAHOOオークションで探して、やっと見つけて落札しました。嬉しかったのですがここからがお笑いです。広帯域のオシロスコープには、もちろん広帯域のプローブが必要です。本体よりも高いプローブを新品で購入しました。しかし中古の4チャンネル広帯域1GHzデジタルオシロスコープと広帯域プローブのおかげで仕事は,はかどりました。これ一台でほとんどの開発が可能です。この時も測定器の偉大さを思い知らされました。測定器の設備をケチってはかえって無駄な操作と思考に明け暮れて無駄な時間を潰し、挙句の果ては納期が遅れる事は、多々あります。オシロスコープ等の計測器は、開発するハードウェアに合った帯域幅の広いもの。そうですね 10倍程度は欲しいですね。使ってみれば分かります!ただし 注意点があります。プローブのグランドはしっかりしたグランド点に接続する事。プローブのグランドは、出来るだけ短くする事です。これを怠るとオーバーシュート、アンダーシュートだらけで本来の波形は見え難くなります。意外と高速ロジック回路でオシロスコープを正しく使いこなす事は難しい事です。すべての基本は、グランドです。銅箔を貼る事はここにあります。昨今の少ない開発予算で高度な開発を要求される設計開発者は、出来るだけハードウェア開発環境を良くして取り組む事がプロジェクトの早期完了に繋がります。ただし すべての測定器を高性能機にする必要はありません。お金の無駄です。開発する物によりますが、特に高速ロジック系は最低限オシロスコープだけは良いものを揃えましょう。ハードウェア設計者は、波形とタイミングが命ですから。特に昨今のオシロスコープは、デジタルオシロなので高性能ロジックアナライザーにもなります?4チャンネルでは、少し不足ですが、基準となる信号が決まれば後はプローブを移動して観測すれば大体は見る事が可能です。何故か?同期式設計ですから。特に昨今の高速のロジックは、同期式です。今回の回路もSDRAM中心ですからCPLDから出て来る信号は、メインクロックに同期しています。だから4チャンネル広帯域1GHzデジタルオシロスコープでロジックアナライザーがわりになるのです。もちろん CPLDの中には非同期回路もありますが、ピンに出して観測する場合は、クロックで充分に同期化してください。

次回は、アプリケーション開発についてお話します。

第2回

ある日、私は会議室に呼ばれアナライザーの開発は、会社としてやらない事に決まりましたと告げられ、貴方はどうしますかと聞かれました。暫く考えて会社を辞めますと答えました。それから自宅でUSBアナライザーの開発が始まりました。試作を行うため秋葉原に通い手配線で回路を組んで試行錯誤の連続です。USB 2.0 は半端な技術では動作しない事は覚悟していましたが、ユニバーサル基板に手配線では、まず動きません。電源と特にGNDの配線は重要です。そこに高速のSDRAMとUSB 2.0の入力回路、FPGA、ローカルCPU、ホスト通信用USB回路を手配線で行い、とりあえず基板が完成しました。一番苦労したのは高速の一次FIFO回路ですが、なぜ必要か? USB 2.0の信号を全部取り込むには、SDRAMの早いアクセスが必要ですがシングル書き込み・読み出しでは、到底間に合いません。どうするか? バースト書き込み方式にすれば解決する事に気が付きました。ただし SDRAMは、リフレッシュ、タイマー書き込み、受信データ書き込み、CPUライトアクセス、CPUリードアクセス、という五つのアクセス処理が必要になります。その間に受信データを待たせる必要があるため、一次FIFOが必要になるのです。この一次FIFOとSDRAMのハードウエアセマフォの完成によって大きくテバッグは進展しました。ただし 使用する部品等をもっと高価な高速な部品にしていたら開発は早かったかもしれません。

しかし 製品開発の目的が廉価で使いやすいを目標にしているため、到底無理な注文です。技術力でカバーしました。いや したと思います。市販価格の半分で販売するためには、これ位の努力は必要です。SDRAMは、色々な動作モードが有りますので初心者には、敷居が高いと思いますが、一度動いてしまうと少々無茶をしても誤動作しません。SRAMと同じような感覚で設計が出来るようになります。ただし クロックの引き回しには注意が必要です。ここまでが一番難関でした。第二の難関は、FPGAの内部設計とデバッグです。価格の安いFPGAを使用したためロジック数の制限と内部配線の制限です。FPGAの中にSDRAMコントローラー、USB 2.0 インターフェース回路、トリガ回路、フィルタ回路、バス制御回路等を一つにしたため、回路を組み込む内にコンパイラーがもうロジックが配線出来ないとギブアップしてきます。それでも回路構成を変更して試行錯誤して何とか収まりましたが、試験信号用として外部にピンを引き出すとまたしてもコンパイラーがエラーを通知します。もう一段の回路構成の変更が必要になりました。 参考までに試作基板の写真を掲載します。

この続きは 次回にお話します。

第1回

私がプロトコルアナライザーと出会ったのは前職で38年位前の事ですが 当時最先端のプロトコルで有ったHDLC通信を使用した公共用端末装置の開発に従事した事でした。その当時の通信速度は9600bpsで専用回線で日本全国にその専用端末は設置されました。私自身もHDLCって何?との認識しか持ち合わせていませんでしたが、相手先企業にはなぜか?専門家として紹介されて戸惑った記憶が有ります。会社が仕事を取りたいためで有ることは明白ですが(すぐにばれました・・笑)それからあらゆるHDLC関連書物を読みあさり何とかプロトコルの理解が出来るようになりましたが、現地での複雑難解なプロトコルのデバッグに非常に苦労しました。それでも何とかデバッグが進み、ホストと端末の通信試験までこぎつけました。そこで私は大きなカルチャーショックを受けました。・・・・何とホスト側は、通信アナライザーを常時接続してデバッグしていたからです。当時HDLC通信アナライザーは、1000万円位だとホスト側担当者から伺って驚きました。それも外国製で全部英語表記でどうやって使うのかさえ分かりませんでした。それでもホスト側担当者のご好意で?アナライザーを借りる事が出来、操作方法を教えて頂きながら端末側のデバッグを夢中で行いました。本当にプロトコルが手に取るように流れているのが実感できたのと同時にバグが取れていく現実に通信アナライザーの有効性を感じた時でした。その時、実は端末側はバグが多すぎてホスト側との通信試験に失敗して非常にあせっていました。・・・・・・それから紆余屈曲を経て無事にシステムを納入しました。

それから5年位が過ぎ、自分で通信アナライザーを作ってみたいという気持ちが湧いてきました。それからは、通信アナライザーの開発オンパレードになりました。10Mbps HDLCアナライザー、ARCNETアナライザー、カーネットアナライザー、CCLINKアナライザー、USBアナライザー、CircLinkアナライザーと現在に続いています。もちろん試験環境込みで・・・

ただ アナライザーの設計・開発を行うには、最新技術の導入がなければ開発できません。一番大きく寄与したのは、言うまでもなく低コストFPGAの出現です。私は、そのころ、あるFPGAメーカーの営業の訪問を受け、これだと思いすぐさまそのFPGAメーカーのFPGAを6個使用して10Mbps HDLCアナライザーの開発に着手して何とか製品化しました。現在はCPLD1個で実現できますが、これも技術の進歩で我々のような開発技術者にとっては夢のような環境です。開発するのに必要な物はその時代の最先端技術と好奇心と情熱ではないでしょうか・・・・・

1回目は、とりとめの無い話ですが私のアナライザー開発動機について書いてみました。

次回は開発苦労話を・・・・・・・・・・・・・・・・・・・・・

![ARCNETの難解な不具合解析に[ArcScan]](https://arcnet-analyzer.com/wp-content/uploads/2022/03/logo20220308-1.png)